摘要:數據采集是完成信號分析、信息處理的必要前提。能夠對高速數據精確采集、信號實(shí)時(shí)處理, 在現場(chǎng)測控系統中起到至關(guān)重要的作用。文章介紹了采用FPGA控制高精度高采樣率的A/D電路對高頻信號實(shí)時(shí)采集, 以ARM處理器做為數據遠程傳輸的控制器, 通過(guò)DM9000實(shí)現高速數據網(wǎng)絡(luò )傳輸, 將數據存儲在遠程PC端。通過(guò)實(shí)驗測試表明, 該高速數據采集遠程實(shí)時(shí)存儲系統可以穩定的采集各類(lèi)高頻信號, 能夠廣泛應用于多種現場(chǎng)測控系統, 具有極大的應用價(jià)值。

關(guān)鍵詞:FPGA; ARM; 高速數據采集;

Abstract:Data acquisition is the necessary premise to complete signal analysis and information processing.It can be used for accurate data collection and signal processing of high-speed data, which plays a crucial role in the field measurement and control system. A/D circuit controlled by FPGA with high precision and sampling rate is used to perform real-time acquisition of high freduency signal, ARM processor as the controller of data remote transmission, high-speed data network transmission are realized by DM9000, store the data in the remote PC.The experimental tests show that the high-speed data acquisition remote real-time storage system can gather all kinds of high frequency signal steadily, can be widely used in a variety of field measurement and control system, has a great application value.

Keyword:FPGA; ARM; high-speed data acquisition;

在故障診斷等現場(chǎng)測控系統中, 高效采集大量原始數據是提取和分析系統運行過(guò)程中各階段不同信號的必要前提, 為后續信號處理提供了重要保證。

目前的數據采集系統種類(lèi)繁多, 一般處理器不能同時(shí)滿(mǎn)足其高速采集、遠程傳輸存儲和實(shí)時(shí)并行處理。FPGA (Field Programmable Gate Array) 是一種大規模現場(chǎng)可編程邏輯門(mén)陣列, 它是作為專(zhuān)用集成電路 (ASIC) 領(lǐng)域中的一種半定制電路而出現的, 既解決了定制電路的不足, 又克服了原有編程器件門(mén)電路數有限的缺點(diǎn)[1-2]。FPGA在高速數據采集和并行算法處理方面具有單片機和DSP所不具備的優(yōu)點(diǎn)。FPGA內部有豐富的可編程邏輯單元、大量的硬件乘法器模塊、充足的I/O引腳資源, 以及多個(gè)鎖相環(huán) (PLL) 可以把系統輸入時(shí)鐘倍頻到幾百兆赫茲, 以提供給系統內部時(shí)序電路使用。采用FP-GA進(jìn)行高速數據采集存儲系統設計, 具有開(kāi)發(fā)周期短、集成度高、功耗低、工作頻率高 (時(shí)鐘延時(shí)為ns級) 、可現場(chǎng)反復編程、可靠性高等一系列優(yōu)點(diǎn)。FPGA和ARM (Advanced RISC Machines) 單獨都可以完成數據采集工作, 但是要想同時(shí)滿(mǎn)足高速數據的并行采集和同步遠程傳輸存儲, 必須把FP-GA和ARM有效的結合起來(lái), 充分發(fā)揮FPGA對高速并行數據的處理優(yōu)勢, 利用ARM與PC機接口實(shí)現數據通過(guò)以太網(wǎng)實(shí)時(shí)遠程傳輸, 具有成本低、可靠性高、穩定性強的優(yōu)點(diǎn)。因此, 在高速實(shí)時(shí)測控領(lǐng)域有著(zhù)非常廣闊的應用前景。

本文設計了基于FPGA+ARM的高速數據采集和遠程傳輸存儲系統。FPGA采用模塊化的設計方法, 利用Verilog HDL硬件語(yǔ)言設計A/D模數轉換控制器和16位并行緩存控制器, 通過(guò)Quartus II和Modelsim對系統的頂層模塊及各子模塊進(jìn)行功能仿真和時(shí)序仿真, 靜態(tài)時(shí)序分析驗證系統設計的合理性。首先FPGA控制AD7622實(shí)現32MSPS數據并行采集, 然后與ARM進(jìn)行DMA方式的高速數據傳輸, 并在linux內核中移植TCP/IP協(xié)議和DM9000網(wǎng)卡的驅動(dòng)編寫(xiě), 最后在PC機上設計SOCKET網(wǎng)絡(luò )接口, 實(shí)現高速數據的實(shí)時(shí)采集和遠程存儲。

1、系統整體設計

高速數據的實(shí)時(shí)并行采集和存儲是信號分析處理的前提, 保證現場(chǎng)測控系統實(shí)時(shí)高效運行。系統輸入端接入寬帶高頻信號傳感器, 利用FPGA實(shí)現高速數據采集, ARM處理器實(shí)現DMA控制器的高速數據傳輸, 輸出端通過(guò)TCP/IP網(wǎng)絡(luò )協(xié)議與PC機實(shí)現網(wǎng)絡(luò )接口通信, 完成高速數據采集與實(shí)時(shí)存儲[3]。

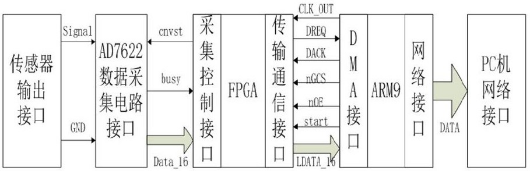

系統的主要硬件結構包括寬帶高頻傳感器、AD7622數據采集模塊、FPGA數據采集主控模塊、ARM9 (S3C2440A) 的DMA控制器模塊、DM9000網(wǎng)絡(luò )傳輸模塊和PC機數據接收的軟件模塊。系統的基本結構如圖1所示。

圖1 系統基本結構圖

高速數據采集與存儲系統實(shí)現的基本功能是利用高頻寬帶傳感器檢測各類(lèi)高頻信號, 經(jīng)過(guò)信號調理電路對采集信號放大、濾波處理。FPGA核心處理器控制AD7622數據采集模塊的初始化設置, 以32MSPS速率并行采樣。在A(yíng)RM的linux內核版本為2.6.25.8操作系統下, 配置數據傳輸方式為內存直接存取 (DMA) 方式, 以及DMA控制器的傳輸方式、服務(wù)模式和請求方式等;移植TCP/IP協(xié)議和編寫(xiě)DM9000網(wǎng)卡驅動(dòng)實(shí)現高速數據實(shí)時(shí)傳輸。在PC機端通過(guò)SOCKET網(wǎng)絡(luò )接口實(shí)現數據接收。最終將大容量的數據寫(xiě)入PC機硬盤(pán)的TXT文件中。

系統硬件接口設計如圖2所示。

圖2 系統硬件接口圖

圖2中, 高頻寬帶傳感器的輸出信號直接傳送給A/D數據采集調理電路的信號接收接口, 并將兩者共地降低干擾。FPGA工作在100Mhz的時(shí)鐘頻率下, 控制AD7622的cnvst啟動(dòng)轉換引腳 (低電平表示啟動(dòng)轉換) , 實(shí)時(shí)檢測busy信號的下降沿 (高電平表示AD7622正在轉換) 。FPGA同時(shí)與ARM的系統總線(xiàn)接口通信, 在A(yíng)RM端設計DMA控制器完成高速數據傳輸, 其中FPGA的16位并行數據輸出給ARM的數據總線(xiàn)LDATA接口, 其它DMA通信用到的信號線(xiàn)包括:DMA外部請求DREQ, DMA外部響應DACK, S3C2440A的存儲器BANK3的使能信號n GCS3和讀寫(xiě)控制信號n EW、n OE, DMA的數據讀寫(xiě)時(shí)鐘CLKOUT和一次單服務(wù)模式DMA開(kāi)始信號start。通過(guò)這些信號控制接口完成FPGA與ARM的DMA方式數據傳輸通信。最后, ARM與PC機通過(guò)有線(xiàn)網(wǎng)絡(luò )接口實(shí)現高速數據實(shí)時(shí)采集存儲。

2、系統軟件設計與仿真

FPGA控制高精度高采樣率的ADC電路, 在高速數據采集的邏輯設計方面具有容量大、處理速度快、集成度高等優(yōu)點(diǎn)。邏輯單元LE是FPGA的基本單元, 也是衡量其容量性能的最重要指標, FPGA通過(guò)四輸入的查找表 (16*1RAM) 實(shí)現組合邏輯的設計, 可現場(chǎng)反復編程[4-5]。為了提高FPGA的運算性能, 芯片制造商在其內部集成了專(zhuān)用硬件乘法器等硬核[6]。DMA (Direct Memory Access) 技術(shù)是一種高速的數據傳輸方式, 允許在外部設備和存儲器之間、存儲器和存儲器之間等直接傳輸數據。當DMA控制器從數據源 (外設和存儲器) 將數據讀到數據總線(xiàn)后, 會(huì )立刻在同一個(gè)DMA周期內把數據直接傳送到目標地址單元內, 而不需要像CPU那樣先接收后轉發(fā)。FPGA控制的數據采集和ARM端控制的DMA方式數據傳輸協(xié)同工作, 高效完成高速數據采集和實(shí)時(shí)同步傳輸。

2.1、高速數據采集模塊的FPGA設計

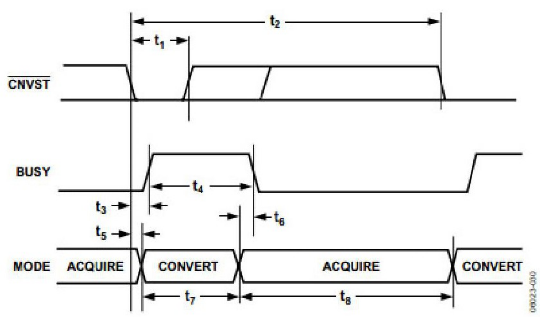

本系統的核心處理器選用Altera公司Cyclone IV系列的FPGA芯片EP40E40F23C6, 系統最高工作頻率為400 Mhz。為了保證不失真的數據采集, 設計AD7622為2MSPS*16bit的并行轉換模式。FP-GA系統時(shí)鐘是外部50 Mhz晶振時(shí)鐘經(jīng)過(guò)內部PLL倍頻之后得到的100 Mhz, 時(shí)鐘周期為10 ns。這樣滿(mǎn)足每50個(gè)時(shí)鐘周期 (500 ns) 完成一次采樣數據轉換。AD7622的數據采集轉換時(shí)序如圖3所示。

圖3 AD7622數據轉換時(shí)序圖

配置AD7622為進(jìn)行連續讀寫(xiě)轉換。AD7622的轉換過(guò)程是:初始化時(shí)CNVST信號線(xiàn)為高電平, BUSY信號線(xiàn)為低電平, 由FPGA控制CNVST輸出4個(gè)周期 (t1時(shí)間) 低電平信號作為AD7622的開(kāi)始轉換啟動(dòng)信號, 當AD7622內部機制檢測到CNVST的低電平時(shí), 令BUSY信號由低電平變?yōu)楦唠娖? 表示正在進(jìn)行單次數據的并行轉換, 同時(shí)PFGA內部以100 Mhz的時(shí)鐘頻率檢測BUSY信號由高變低的下降沿, 來(lái)判斷單次數據轉換完成。利用Quartus II和Modelsim對數據采集模塊進(jìn)行時(shí)序仿真[7], 結果如圖4所示。

圖4 Modelsim數據采集模塊時(shí)序仿真圖

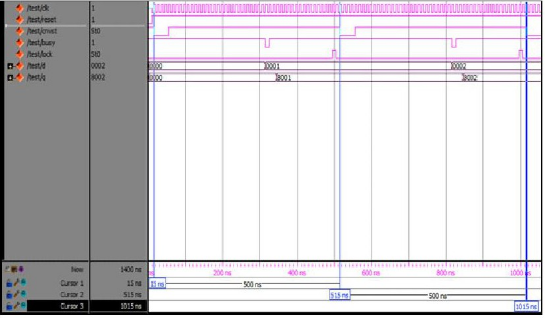

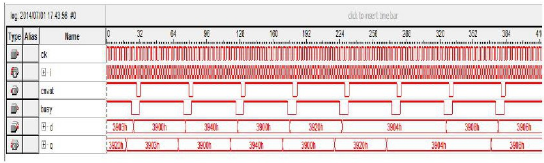

圖4中, clk為100 Mhz的系統時(shí)鐘;reset為復位信號 (低電平有效) ;32MSPS的采樣率下, 一個(gè)采樣周期為50個(gè)時(shí)鐘 (500 ns) , cnvst前4個(gè)時(shí)鐘周期為低電平;busy在第36個(gè)時(shí)鐘周期出現下降沿, 表示一次數據轉換完成;lock在每次采樣周期結束時(shí)為高電平, 表示采樣完成;d[15:0]表示16位的AD7622輸出信號;q[15:0]表示FPGA的讀取信號。利用嵌入式邏輯分析儀 (Signal Tap II Logic Analyzer) 對AD7622數據采集卡的測試結果如圖5所示。

圖5 AD7622數據采集硬件測試結果圖

對AD7622數據采集模塊進(jìn)行驗證, 首先將傳感器信號輸出到數據采集模塊的輸入端, 并把數據采集模塊的十六位數字信號和轉換控制信號連接到FPGA的GPIO接口, 因為傳感器實(shí)際輸出經(jīng)過(guò)信號調理電路濾波、衰減, 最終轉換信號的幅值為0.9 V左右, 滿(mǎn)足AD7622差分輸入范圍。圖5中, 經(jīng)過(guò)試驗測試采集到的數字信號以二進(jìn)制補碼編碼, 并以十六進(jìn)制顯示。由于A(yíng)D7622的基準電壓是2.048 V, 所以電壓值的最小分辨率是62.5 u V。經(jīng)過(guò)換算, 十六進(jìn)制3900H轉換成實(shí)際模擬電壓是0.912 V, 符合高速數據采集的設計要求。

2.2、數據傳輸模塊的DMA設計

DMA控制器既是一個(gè)具有系統總線(xiàn)控制能力的主控部件, 又是一個(gè)工作方式必須由CPU進(jìn)行設置的受控部件。受控部件需要由CPU對它進(jìn)行工作方式的設置, 以確定通道的選擇、數據傳輸模式及類(lèi)型、內存區域的首地址、地址是遞增或遞減、傳送的總字節數等[8]。主控部件掌握總線(xiàn), 可以產(chǎn)生尋址存儲器的地址信號以及進(jìn)行數據讀寫(xiě)的控制信號。DMA方式傳輸與CPU共享系統總線(xiàn), 對于I/O設備進(jìn)行快速數據傳輸, 必須采用DMA方式實(shí)現。

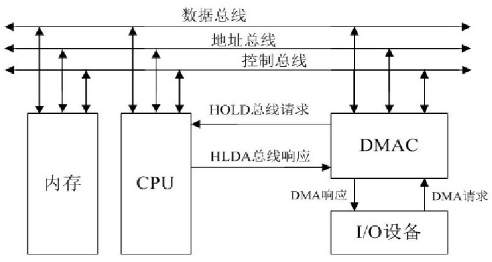

DMA數據傳輸的整體結構如圖6所示。

圖6 DMA數據傳輸的整體結構

DMAC (DMA控制器) 是數據傳輸的核心電路, HOLD和HLDA用于DMA方式請求和響應。DMA數據傳輸過(guò)程一般分為如下四個(gè)階段:申請階段、響應階段、數據傳送階段和傳送結束階段。

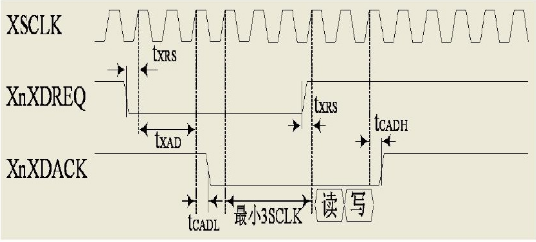

S3C2440A處理器擁有4個(gè)獨立通道的DMA控制器, 每個(gè)DMA通道都有6個(gè)源, DMA的觸發(fā)方式分為軟件觸發(fā)和硬件觸發(fā)。本文選用的是DMA通道0, 源為n XDREQ0, DMA的操作方式選擇為源設備和目的設備都在系統總線(xiàn)上, 采用H/W請求模式 (硬件請求模式) , 數據的傳輸模式設置為單服務(wù)傳輸模式。DMA的硬件請求時(shí)序圖如圖7所示。

圖7 DMA的硬件請求時(shí)序圖

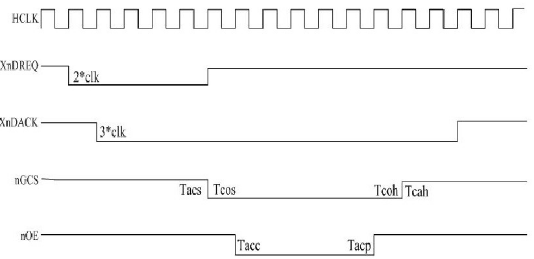

S3C2440A的DMA通道0共有9個(gè)控制寄存器, 其中6個(gè)用于控制DMA傳輸, 3個(gè)用于監視DMA控制器的狀態(tài)。通過(guò)在Linux系統中, 配置DMA控制寄存器、S3C2440A的存儲器、BNAK選擇控制寄存器和時(shí)鐘控制寄存器, 繼而控制DMA的運行時(shí)鐘CLKOUT、外部響應Xn DACK的延時(shí)、BANK選通信號n GCS的建立時(shí)間和延遲時(shí)間以及讀寫(xiě)使能信號n OE的建立時(shí)間和延遲時(shí)間。基于FPGA和ARM的DMA通信時(shí)序圖如圖8所示。

圖8 基于FPGA和ARM9的DMA通信時(shí)序圖

圖8中, HCLK是ARM9提供的用于DMA傳輸的時(shí)鐘100Mhz, Xn DREQ是FPGA向ARM9發(fā)送DMA請求的外部信號, Xn DACK是ARM9接收到外部DMA請求后的響應信號, n GCS是S3C2440A存儲器BANK3的選通信號, n OE是系統存儲單元讀信號的使能端, 通過(guò)以上方式實(shí)現DMA的有效傳輸。

3、系統的具體實(shí)現

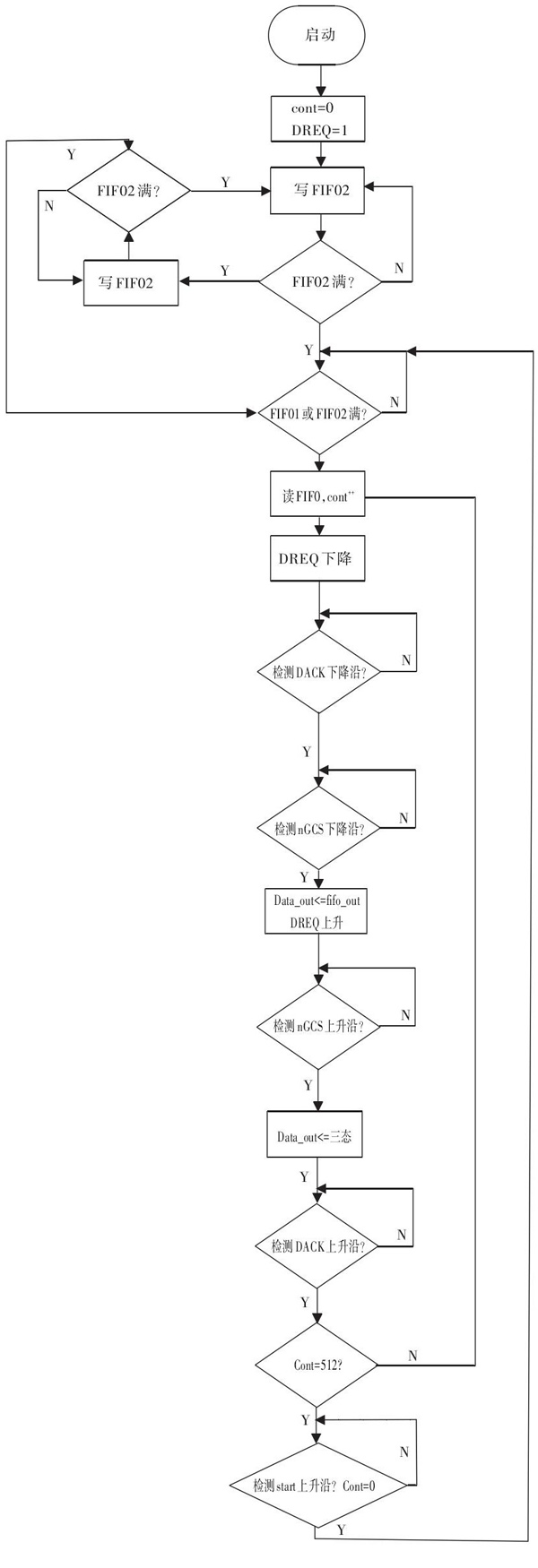

高速數據采集存儲子系統利用FPGA和ARM開(kāi)發(fā)平臺聯(lián)合實(shí)現, FPGA和ARM采用DMA的方式進(jìn)行高速數據傳輸, 并在FPGA內部采用雙乒乓緩存的異步FIFO解決數據采集和數據傳輸的同步進(jìn)行[11]。當系統上電啟動(dòng)時(shí), 首先在FPGA內部利用Verilog HDL硬件編程語(yǔ)言初始化各端口的值, 令FIFO的計數個(gè)數初值count=0, DMA外部硬件請求端DREQ=1, 初始化之后開(kāi)始數據采集, 控制AD7622的數據轉換, 把每次轉換完成的16位數字量存在預先定義的16bit*512的FIFO1, 直到FIFO1存滿(mǎn)了之后開(kāi)始讀, 并且令DREQ產(chǎn)生下降沿, 計數器計數count++, 同時(shí)實(shí)時(shí)采集的數據存到另一個(gè)16bit*512的FIFO2, 這樣保證數據采集能實(shí)時(shí)連續進(jìn)行。每當FPGA發(fā)生一次DREQ的下降沿請求時(shí), ARM的DMA控制器立即檢測到外部請求并申請系統總線(xiàn), 申請成功便產(chǎn)生DACK的下降沿作為DMA的響應信號, FPGA在200 Mhz時(shí)鐘下檢測DACK的下降沿, 同時(shí)檢測n GCS和n OE的低有效信號, 只有當ARM端DMA操作內存選通并可以讀寫(xiě)時(shí), FPGA才把從FIFO讀出的數據放到ARM系統總線(xiàn)的數據總線(xiàn)端口, 其他時(shí)刻令數據總線(xiàn)端電平為高阻態(tài), 保證系統總線(xiàn)讀取數據不受污染[9-10]。FPGA內部FIFO的讀時(shí)鐘是由S3C2440經(jīng)過(guò)倍頻配置, 通過(guò)時(shí)鐘輸出引腳CLKOUT提供, 時(shí)鐘頻率為100 Mhz。直到ARM的DMA操作完成512次 (count=512) 之后, 把count清零, 此時(shí)FPGA不斷檢測ARM發(fā)送的下次傳送啟動(dòng)信號start的上升沿, 當檢測到了下一次啟動(dòng)傳輸信號, 便開(kāi)始下一個(gè)512次DMA的數據傳送。FPGA和ARM9實(shí)現DMA數據傳輸的流程圖如圖9所示。

圖9 FPGA和ARM9的DMA傳輸流程圖

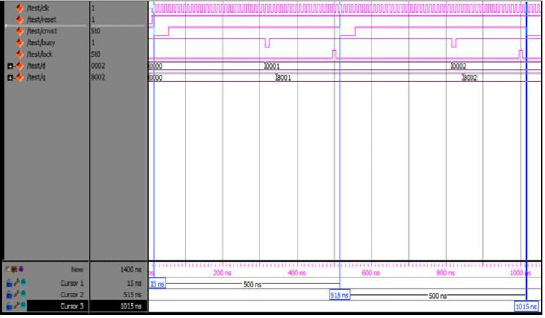

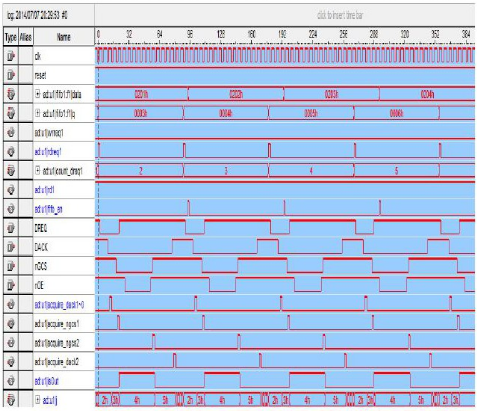

高速數據采集存儲子系統設計的關(guān)鍵是FPGA與ARM9的DMA通信。FPGA驅動(dòng)程序的設計主要包括:AD7622采集卡的驅動(dòng)程序設計, 乒乓緩存FIFO的時(shí)序控制, 與ARM進(jìn)行DMA通信的時(shí)序控制。ARM系統的重點(diǎn)工作主要包括:Linux系統內部存儲器BANK單元的配置, GPIO端口寄存器的配置, DMA相關(guān)寄存器的配置, TCP/IP協(xié)議的移植, DM9000網(wǎng)卡驅動(dòng)程序的設計, PC機接收數據是通過(guò)SOCKET網(wǎng)絡(luò )接口實(shí)現。FPGA和ARM作為一個(gè)整體協(xié)同工作, 相互配合發(fā)揮各自的優(yōu)勢, 完成高速數據實(shí)時(shí)采集, 動(dòng)態(tài)傳輸存儲和控制管理等, 為后續的軟件分析處理提供保障。利用Quartus II內部的Singal Tap II Analyzer對系統性能進(jìn)行分析與驗證, 系統工作時(shí)序圖如圖10所示。

圖1 0 FPGA與ARM的DMA通信測試時(shí)序圖

圖10中, clk為FPGA工作時(shí)鐘100 Mhz;reset為復位信號, 低電平有效;data為AD7622的輸出數據;q為FPGA的采集信號;rereq和wrreq為FIFO的讀寫(xiě)信號;count_dreq為DMA傳輸數據的個(gè)數;DREQ、DACK、n GCS、n OE為DMA的傳輸控制信號;其他信號為FPGA內部溝通信號。由圖可知, DMA方式的數據傳輸滿(mǎn)足32MSPS采樣率下高速數據的實(shí)時(shí)傳輸, 達到系統的設計要求。

4、結論

本文分析了FPGA和ARM分別在高速數據采集和處理方面的優(yōu)缺點(diǎn), 結合整個(gè)系統需要實(shí)時(shí)同步傳輸數據, 最終采用FPGA做為數據采集核心控制器, ARM做為數據DMA方式傳輸的控制器, 通過(guò)與PC機的網(wǎng)絡(luò )接口連接, 實(shí)現并行采集和實(shí)時(shí)同步傳輸。

整個(gè)系統的硬件接口的設計思路具有很強的通用性, 也可以廣泛應用于各種高速低速信號的采集, 用戶(hù)方便修改升級, 具有很強的實(shí)用性。

參考文獻

[1]鄧志陽(yáng), 曹玉雯, 祝海江.一種基于FPGA的超聲信號高速采集與壓縮方法[J].計量技術(shù), 2010 (1) :27-29.

[2]于宗光, 魏敬和, 王國章.SoC和FPGA技術(shù)未來(lái)的發(fā)展趨勢[J].電子與封裝, 2006, 6 (3) :1-5.

[3]朱建光, 余紅英.基于A(yíng)RM和FPGA的高速數據采集系統[J].伺服控制, 2010 (3) :75-77.

[4]麥曉明, 王銳, 陳海涵, 等.輸電線(xiàn)路無(wú)人機巡檢數據鏈路通信系統設計[J].廣東電力, 2014, 27 (4) :76-81.

[5]張曉娟.基于FPGA的實(shí)時(shí)視頻信號處理系統的設計[D].太原:太原理工大學(xué), 2012.

[6]郝宇寧.基于DSP的小波分析在聲發(fā)射信號處理中的應用研究[D].南寧:廣西大學(xué), 2007.

[7]鄔琦, 楊江濤, 馬喜宏.基于FPGA的高速信號采集電路的設計與實(shí)現[J].實(shí)驗室研究與探索, 2015, 34 (4) :124-128.

[8]甘利軍.裝甲車(chē)發(fā)動(dòng)機檢測與故障診斷設備的研究[D].武漢:武漢理工大學(xué), 2009.

[9]張偉, 劉爽, 王炳義, 等.基于A(yíng)RM的CCD數據遠程采集系統設計[J].微計算機信息, 2009, 25 (4) :89-90.

[10]王珊.基于A(yíng)RM9的近程無(wú)人機數據采集系統[J].測控遙感與導航定位, 2013, 43 (8) :40-43.

[11]施華鈞.高效異步FIFO的設計實(shí)現[D].長(cháng)沙:湖南大學(xué), 2013.