摘要:隨著(zhù)設計工藝的飛速發(fā)展, SRAM型FPGA的規模也越做越大, 對配置芯片的存儲容量、配置速度提出了更高的要求。基于SRAM型FPGA, 采用BPI接口和大容量FLASH, 并通過(guò)JTAG接口轉BPI接口的軟核, 代替傳統配置芯片內部的JTAG模塊, 完成了基于SRAM型FPGA的配置芯片設計, 其結構簡(jiǎn)單、芯片面積小、存儲容量大、速度快, 兼容性好。通過(guò)數字仿真波形分析和FPGA原型驗證, 驗證了設計方法的可行性和正確性。

關(guān)鍵詞:配置芯片; JTAG; FLASH; FPGA; BPI; 軟核;

Abstract:With the rapid development of the design process, the size of the SRAM-type FPGA is getting bigger and bigger, putting higher requirements on the storage capacity and the configuration speed of the configuration chip. In this paper, based on the SRAM-type FPGA, using high-capacity FLASH and BPI interface, and the soft core of JTAG interface to BPI interface through FPGA instantiation instead of the JTAG module of traditional configuration chip, the design of configure chip based on SRAM-type FPGA have been completed. This design has realized the simple design structure, small chip area, storage capacity, speed, compatibility. The feasibility and correctness of the design method is proved through the analysis of corresponding digital simulation waveform and FPGA prototype verification.

Keyword:configuration; JTAG; FLASH; FPGA; BPI; soft core;

1、引言

基于SRAM結構的FPGA, 上電時(shí)要將配置數據讀入到片內SRAM中, 配置完成就可以進(jìn)入工作狀態(tài)。掉電后SRAM中的配置數據丟失, FPGA內部邏輯關(guān)系隨之消失。正常使用SRAM型FPGA時(shí)必須配一個(gè)配置芯片用來(lái)存儲配置數據, 上電后FPGA能快速從配置芯片內加載到配置數據, 使FPGA正常工作。隨著(zhù)設計工藝的飛速發(fā)展, FPGA規模也越做越大, 配置容量也呈幾何倍數增長(cháng), 因而對配置芯片的配置便捷性、加載速度、存儲容量提出了更高的要求[1]。本文基于SRAM型FPGA, 設計一款改進(jìn)型配置芯片, 該芯片兼容傳統的配置芯片。

2、配置芯片下載方式

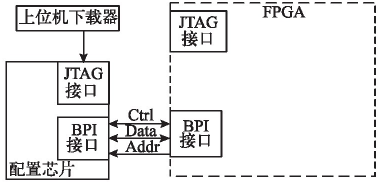

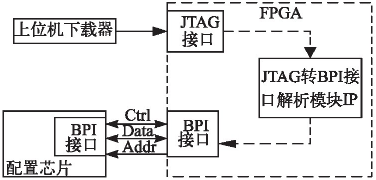

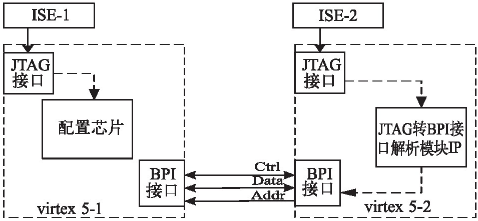

配置芯片都是與SRAM型FPGA搭載使用, 一般一片SRAM型FPGA會(huì )搭載一片配置芯片或多片配置芯片級聯(lián)使用。因此我們在對配置芯片加載數據時(shí)可以借助FPGA來(lái)完成。普通配置芯片下載方式[2]如圖1所示, 通過(guò)上位機軟件建立FPGA工程、編譯、布局布線(xiàn)后生成配置數據, 連接JTAG下載至配置芯片, FPGA再通過(guò)BPI接口從配置芯片中加載配置數據。改進(jìn)型配置芯片下載方式如圖2所示, 配置芯片去除了JTAG模塊, 通過(guò)例化一個(gè)JTAG轉BPI的軟核在FPGA內部實(shí)現。上位機可以通過(guò)連接FPGA的JTAG再通過(guò)軟核轉換為BPI格式的數據下載配置芯片, 這樣可以在不提供額外硬件資源的前提下, 實(shí)現用JTAG接口對配置芯片的讀寫(xiě)。上位機也可以通過(guò)BPI接口直接對配置芯片讀寫(xiě)數據, BPI的數據總線(xiàn)為16位寬, 數據傳輸量大, 最高配置速度為800 Mb/s。配置芯片的下載方式?jīng)Q定了配置芯片的架構設計。

本設計的優(yōu)點(diǎn)如下:

(1) 不需要JTAG模塊, 省去配置芯片的大部分控制邏輯, 減少流片風(fēng)險;

(2) 在不增加硬件資源的前提下, 直接通過(guò)設計一個(gè)JTAG接口轉BPI接口的軟核, 通過(guò)FPGA生成對應的電路, 仍能保留JTAG下載及調試配置芯片的功能;

(3) 兼容以往配置芯片的功能。

圖1 普通配置芯片下載框圖

圖2 改進(jìn)型配置芯片下載框圖

3、設計與實(shí)現

3.1、配置芯片架構設計

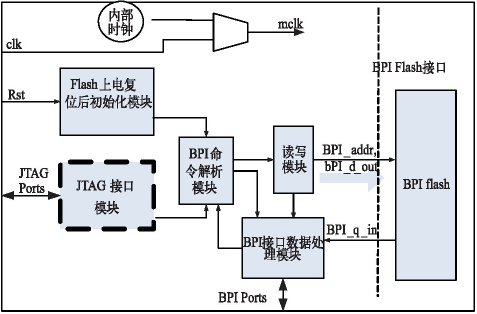

如圖3所示, 配置芯片由初始化模塊、JTAG接口模塊、BPI命令解析模塊、Flash讀寫(xiě)模塊、接口數據處理模塊及Flash組成。上電后由內部時(shí)鐘供給初始化模塊, 讀取Flash的一些配置信息, 保證每個(gè)Flash地址都可以正確讀寫(xiě)。當初始化結束后, 就可以根據JTAG接口或者BPI接口接收數據。JTAG接口模塊是一種符合JTAG接口協(xié)議、能解析數據命令、下載、調試配置芯片的一個(gè)接口模塊[3]。BPI接口數據處理模塊通過(guò)BPI控制信號獲得數據總線(xiàn)及地址總線(xiàn)上的數據。通過(guò)兩個(gè)接口接收到的數據和地址由BPI命令解析模塊解析具體對Flash的操作并傳給Flash讀寫(xiě)模塊[4], 能產(chǎn)生有效的讀寫(xiě)時(shí)序對Flash進(jìn)行讀寫(xiě)。本文把圖3中用虛線(xiàn)畫(huà)的JTAG接口模塊省去, 把這部分邏輯改為用FPGA的軟核實(shí)現。

圖3 配置芯片架構

3.2、軟核設計

如圖4所示, 軟核設計思路是:開(kāi)始TMS信號經(jīng)過(guò)狀態(tài)機解析當前TDI是數據還是命令, 根據數據或者命令分別把TDI的數據存儲到數據寄存器和指令寄存器;再進(jìn)一步根據指令和數據解析成BPI對應的地址或者數據, 還有BPI的控制信號線(xiàn)。當解析到是讀數據命令或者讀狀態(tài)命令, 可以根據BPI接口的DATA總線(xiàn)讀到數據緩存器通過(guò)TDO輸出。

圖4 軟核框圖

3.3、配置命令定義

如表1所示, BA是指塊地址, 一個(gè)塊地址包括1 Mbits;BLA是指一個(gè)單位的地址, 一個(gè)地址存儲16 bits;CRD是指配置數據;SDR是指返回的狀態(tài)數據;PD是指寫(xiě)命令時(shí)每個(gè)地址對應寫(xiě)入的數據;RD是指讀命令時(shí)讀出的數據。每個(gè)命令都需兩個(gè)有效周期完成, 讀命令不需要具體的命令值, 只要BPI接口的FOE信號直接拉低就可以, 這樣做是為了方便FPGA上電完自動(dòng)去加載配置芯片內的配置數據, 省去發(fā)讀命令的操作。

表1 配置芯片命令

3.4 、擦除時(shí)序設計

如圖5所示, 第一個(gè)寫(xiě)周期數據總線(xiàn)發(fā)送20h命令, 地址總線(xiàn)發(fā)送對應要擦除的區域地址, 第二個(gè)寫(xiě)周期數據總線(xiàn)發(fā)送D0h命令, 地址總線(xiàn)不變, 當擦除完成后數據總線(xiàn)會(huì )返回一個(gè)80h的狀態(tài), 如未擦除完成會(huì )返回00h的狀態(tài)。

圖5 擦除時(shí)序

3.5、寫(xiě)時(shí)序設計

如圖6所示, 第一個(gè)寫(xiě)周期數據總線(xiàn)發(fā)送40h命令, 地址總線(xiàn)發(fā)送對應要寫(xiě)數據的地址, 第二個(gè)寫(xiě)周期數據總線(xiàn)發(fā)送要寫(xiě)入的數據, 地址總線(xiàn)不變, 當寫(xiě)入完成后數據總線(xiàn)會(huì )返回一個(gè)80h的狀態(tài), 如未寫(xiě)完成會(huì )返回00h的狀態(tài)。

圖6 寫(xiě)時(shí)序

3.6、讀時(shí)序設計

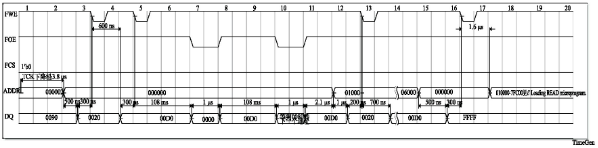

如圖7所示, 第一個(gè)寫(xiě)周期FOE_B拉低, FEW_B為高, 就說(shuō)明是讀命令, 每一個(gè)地址都需立即返回一個(gè)該地址的數據。

圖7 讀時(shí)序

4、仿真驗證

采用基于verilog行為級描述的RTL代碼, 建立整個(gè)仿真驗證環(huán)境, 利用Cadence公司仿真工具NC進(jìn)行設計仿真驗證[5], 對配置芯片進(jìn)行BPI接口數據仿真, 對配置芯片接軟核進(jìn)行FPGA原型驗證。

4.1、配置芯片加載FPGA EDA

如圖8所示, 通過(guò)配置芯片與FPGA對接, 通過(guò)仿真波形看到done信號已經(jīng)由低變高, 說(shuō)明配置芯片內的數據已經(jīng)正確無(wú)誤地加載到FPGA內。

圖8 配置芯片加載FPGA時(shí)序

4.2、配置芯片原型驗證

如圖9所示, 通過(guò)用兩片xilinx virtex5 95T芯片來(lái)完成整個(gè)配置芯片的FPGA驗證。先通過(guò)ISE-1軟件把設計好的配置芯片工程load到Virtex5-1中, 此時(shí)virtex-1就實(shí)現了配置芯片的功能, 再通過(guò)ISE-2軟件下載一個(gè)JTAG轉BPI接口的軟核給virtex5-2, 再通過(guò)ISE-2建立一個(gè)工程, 通過(guò)JTAG接口下載給virtex5-2, 下載的數據通過(guò)轉換后對virtex5-1進(jìn)行寫(xiě)入配置數據, 當把全部數據寫(xiě)完后, ISE-2對virtex5-2進(jìn)行復位, 放開(kāi)對virtex5-2的控制權限, 再重新上完電后, virtex5-2會(huì )自動(dòng)從virtex5-1內加載配置數據, 直到加載結束Done接的燈亮。Done信號變高代表配置數據已正確無(wú)誤地下載到FPGA內, FPGA對應的工程可以正常啟動(dòng)。

圖9 配置芯片FPGA驗證框圖

5、結論

本文基于SRAM型FPGA設計的配置芯片, 設計結構簡(jiǎn)單, Flash容量大, 通過(guò)BPI接口訪(fǎng)問(wèn)速度快, 在不需要更多硬件資源的情況下能兼容以前版本的配置芯片。通過(guò)EDA驗證和FPGA原型驗證, 結果符合預期。

參考文獻

[1]石雪梅, 計賢春.FPGA配置芯片測試方法的研究與實(shí)現[J].計算機與數字工程, 2010, 38 (09) :77-79, 87.

[2]劉笑嫘, 何廣平.FPGA芯片的配置與下載[J].科技信息, 2011, (15) :109-110.

[3]呂彩霞.JTAG的設計與研究[D].北京:北京交通大學(xué), 2006.

[4]潘立陽(yáng), 朱鈞.Flash存儲器技術(shù)與發(fā)展[J].微電子學(xué), 2002 (01) .

[5] (美) Rabaey, J M.數字集成電路-電路、系統與設計 (第二版) [M].周潤德, 等譯.北京:電子工業(yè)出版社, 2004:319-357.